Gollywhomper

A simulator of the SpiNNaker million-core super computer being built at the University of Manchester. This simulator was built as part of the COMP6062b Future Multicore Systems course and investigates the effects of the newly developed circuit board to circuit board connections currently being added to SpiNNaker.

- The simulator is available on GitHub

- A short (5 page) paper is available which describes the simulator and the results obtained aimed at a general Computer Science audience.

- An extended paper is available which describes the system in further detail.

Short Paper Abstract

The SpiNNaker project aims to produce a massively parallel computer containing one million low-power processor cores for running neural simulations in real-time. The system consists of up to 1,200 circuit boards each hosting 48 18-core SpiNNaker chips. The boards are connected via high-speed serial links which multiplex multiple chip-to-chip connections across board boundaries. A model of SpiNNaker was built to asses the effects of these high-speed links on data transmission latency. Our results show that an 80% overhead is introduced by the links caused in part by the naive routing scheme for which some improvements are suggested.

Noteable Figures

The following figures are duplicated from the papers here to serve as an extended abstract.

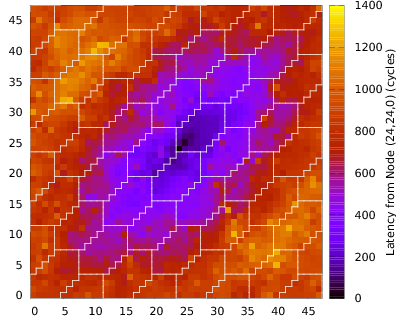

New Link's Effects on Packet Latency

The heatmap below shows how the latencies vary across an idle system from a single point in the center. It can be seen that where board boundaries (shown in white) are crossed there is a general increase in latency. Because of this, the contours are visibly distorted from the expected hexagonal shape. This is particularly visible at the bottom left and top right of the figure.

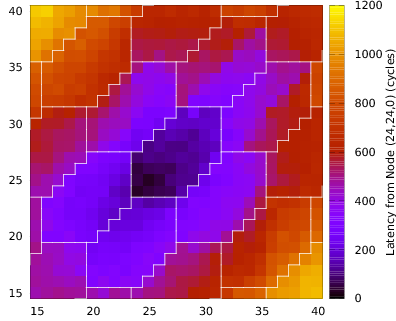

A step in latency is also visible within individual boards as can be seen in the closeup of the above figure shown below. Here there are clear edges where the dimension order routing traverses the dimensions in an order which incurs an extra board crossing. This effect is visible as a step-change in latency along the diagonals of the upper-right boards.

These effects are the reason for the 80% overhead in packet latencies.

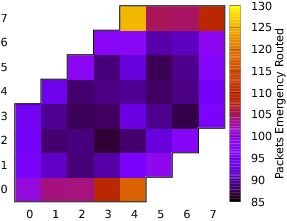

Emergency Routing

It was noted that emergency routing use is incrased for chips on board boundaries (especially on the North and South edges) compared chips within the board.

The reason for this is not yet known and may be due to an error in the simulated model.